郭柏儀博士 劉柏村教授

近年來顯示器已朝向高解析度發展,當顯示螢幕尺寸固定時,解析度的提高代表畫素尺寸的縮小,一般顯示器規格著重於單位英吋中畫素數目(Pixel Per Inch, PPI)的高低。以目前手機而言,顯示螢幕規格已高達800-900 PPI,意味一畫素尺寸只有約30微米的大小。於此範圍內將包含電容,液晶單元或有機發光二極體與多個薄膜電晶體,因此需將薄膜電晶體的尺寸盡量縮小,但也會因此減少電晶體的輸出電流,使顯示畫素充電時間不足與亮度降低。但面對未來解析度的持續提高與閘極驅動電路陣列(Gate on Array, GOA)技術需求,發展具有更高載子遷移率之薄膜電晶體技術乃是當務之急。除了解析度上的演進之外,面板廠在電路層面上為提升獲利能力而漸漸淘汰傳統設計,開始利用薄膜電晶體設計電路來取代IC驅動系統。目前業界已廣泛採用閘極驅動電路陣列 (Gate driver on array; GOA)技術,此方式有助於減少周邊驅動IC成本以及金屬繞線面積以利於高解析度極窄邊框面板的設計。然而,若要將上述面板技術發展的趨勢結合目前薄膜電晶體驅動技術,不同種類的電晶體皆有相對應的困難點必須突破。例如:複晶矽薄膜電晶體(Poly-Si TFTs)雖然可以製作互補式架構以利於電路設計,但其製程條件上需要較多的程序處理使得相對成本較高,而非晶矽薄膜電晶體(a-Si TFTs)和氧化物半導體薄膜電晶體(Oxide Semiconductor TFTs)多半為N型通道電晶體,缺乏互補式架構不利於電路設計等等。然而,如要將薄膜電晶體技術應用到面板周邊驅動電路上,並且達到低成本、高效能以及窄邊框的系統面板要求,則必須同時兼俱互補式電路架構、高電流驅動力、低漏電且製程程序較少等優點才能夠實現此目標。

因此本研究團隊提出將具高載子遷移低漏電N型氧化物半導體薄膜電晶體搭配高效能P型複晶矽薄膜電晶體之異質半導體材料所建構而成的混合互補式薄膜電晶體(Hybrid Complementary TFTs; HC-TFTs)可望同時滿足未來面板技術發展的趨勢。相較於傳統使用全複晶矽薄膜電晶體組成的互補式架構(Poly-Si Based CTFTs ),HC-TFTs架構中所引入的氧化物半導體薄膜電晶體擁有較低的元件漏電流,在面板周邊電路的應用上可使得靜態功耗降低,更有利於節能目標的實現。本研究論文在N型氧化物半導體薄膜電晶體技術方面,已成功利用類二維(2D-like)奈米薄片(Nano Sheet; NS)與無接面(Junctiomless; JL)的結構,發展出兼具低操作偏壓與高效能薄膜型顯示元件,在本技術中,我們開發非晶氧化銦鎢奈米薄片無接面電晶體(a-IWO NS-JLTs),以奈米薄片通道結構阻斷電晶體元件中源極與汲極之間的漏電路徑,進而抑制元件尺寸縮小所造成的不理想短通道效應,並具有近理想之次臨界擺幅(Subthreshold Swing, S.S.)。在P型複晶矽薄膜電晶體技術方面,我們也成功利用新穎低金屬汙染鎳側向誘發結晶技術(Low Metal Contamination Nickel-Induced-Lateral-Crystallization; LC-NILC)製作出具有低漏電流的P型複晶矽薄膜電晶體元件。LC-NILC技術是利用鎳沉積於非晶矽表面,和矽反應生成金屬矽化物,加熱驅使鎳擴散到矽內部,由於鎳的晶格常數和矽相近,當鎳擴散會使矽結晶,藉此來降低複晶矽的結晶溫度,另外,由於我們在鎳沉積於非晶矽表面後就立即將之除去,實驗研究結果已顯示LC-NILC技術能夠有效的降低複晶矽薄膜中鎳金屬汙染物的含量,並提高薄膜元件的特性以及操作可靠度。茲將本研究論文的特點,節錄說明如下 :

1. 類二維(2D-like)非晶氧化銦鎢(a-IWO)奈米薄片(NS)通道:

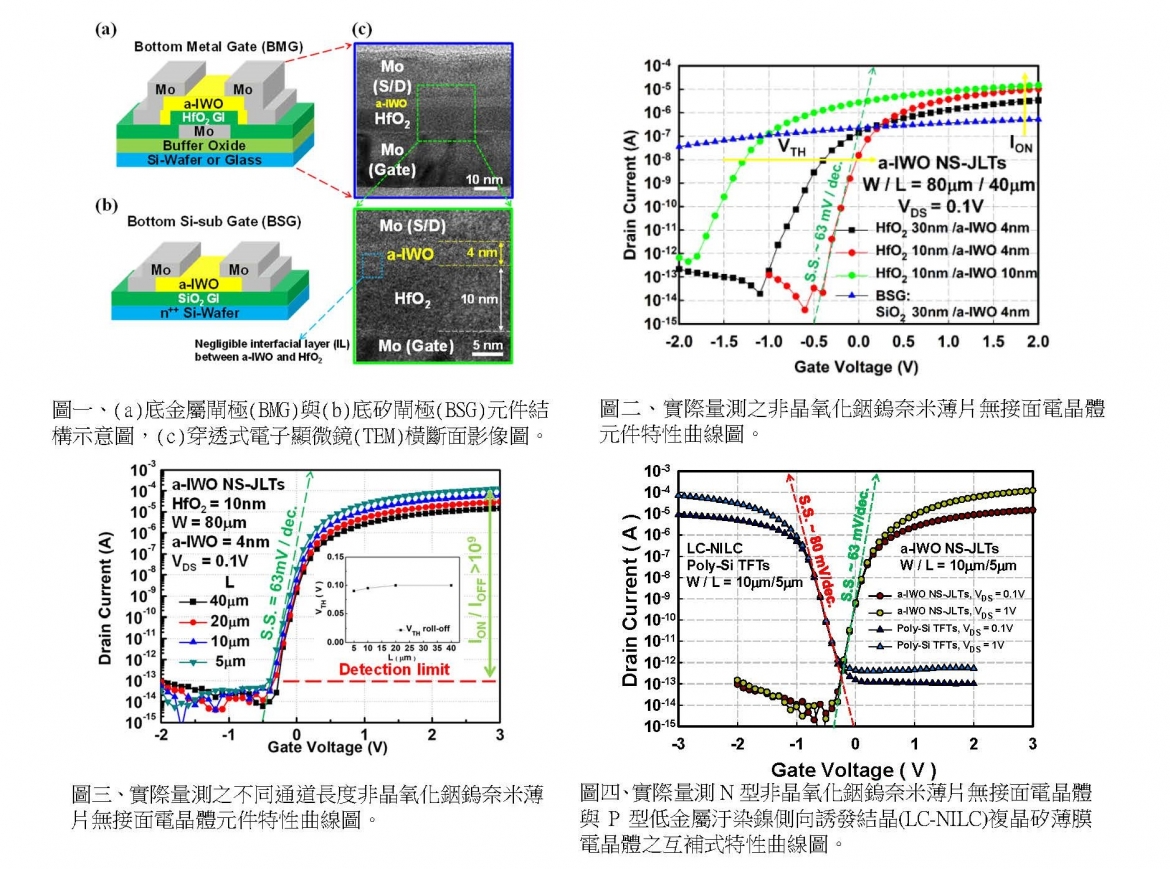

我們製作出兩種不同結構之非晶氧化銦鎢奈米薄片無接面電晶體,如圖一所示,其中圖一(a)為底金屬閘極(Bottom Metal Gate; BMG)元件結構示意圖,是使用鉬做為底閘電極,以二氧化鉿(HfO2)做為閘極絕緣層,圖一(b)為底矽閘極(Bottom Silicon Gate; BSG)元件結構示意圖,是使用n+ 型重摻雜矽基板做為底閘電極,以二氧化矽(SiO2)熱氧化層為閘極絕緣層。圖一(c)為穿透式電子顯微鏡(TEM)橫斷面影像圖,圖中可看見非晶氧化銦鎢奈米薄片通道厚度約為4nm。

2. 具近理想次臨界擺幅之非晶氧化銦鎢奈米薄片無接面電晶體:

圖二為實際量測之非晶氧化銦鎢奈米薄片無接面電晶體元件特性曲線圖,可觀察出整體採用二氧化鉿閘極絕緣層的BMG元件其次臨界擺幅(S.S.)與元件開關特性表現最佳。這是因為二氧化鉿為一種高介電常數(high-k)材料,可提供閘極更加的通道控制能力並使元件的操作電壓降低至 -2V~2V。其中最值得注意的是,當我們微縮二氧化鉿閘極絕緣層厚度至10nm且非晶氧化銦鎢主動層厚度至4nm時,元件具有最大的導通/關閉電流比(ON/OFF Currents ratio; ION/IOFF)、近理想的次臨界擺幅(S.S.) ~ 63mV/dec.與最正值的臨界電壓(Threshold Voltage; VTH)。

3. 具低漏電與低操作偏壓之短通道非晶氧化銦鎢奈米薄片無接面電晶體:

圖三為實際量測之不同通道長度非晶氧化銦鎢奈米薄片無接面電晶體元件特性曲線圖,可以觀察到隨著通道長度微縮,臨界電壓的偏負趨勢之程度相當輕微,這表示奈米薄片通道能成功地抑制短通道效應,其中值得注意的是,隨著元件通道微縮,元件的漏電並不會明顯上升,而通道導通電流則會隨著通道長度微縮而成比例上升,在閘極操作偏壓為3V下,其導通/關閉電流比(ION/IOFF)可高達109以上。

4. 具對稱之混合互補式薄膜電晶體(HC-TFTs)特性:

圖四為實際量測N型非晶氧化銦鎢奈米薄片無接面電晶體與P型低金屬汙染鎳側向誘發結晶(LC-NILC)複晶矽薄膜電晶體之互補式特性曲線圖,可以清楚地觀察到N型與P型元件具相當對稱與匹配的電性,並均表現出低偏壓操作與低漏電流,相信未來實現之混合互補式薄膜電晶體(HC-TFTs)反向器電路具有低偏壓操作與低功耗的目標。

*本研究成果已刊登於國際頂尖會議 2018 VLSI (P. Y. Kuo, P. T. Liu et al., in VLSI Symp. Tech. Dig., Jun. 2018, pp. 21-22),以及自然期刊(Nature)系列的《科學報告(Scientific Reports)》(P. Y. Kuo, P. T. Liu et al., Scientific Reports, vol. 9, No. 7579, May 2019)