突破處理器運算限制 – 光子處理器

洪敦耀, 鄒志偉

近年來人工智慧、雲端運算與大數據等應用的急速發展,對於高速傳輸數據的需求也越來越高。在傳統的積體電路中,透過不斷的將元件縮小來使得單位面積的電子元件密度上升來提升速度,但隨著元件越來越小,傳統的積體電路正在逐漸面臨製程上的物理極限,逐漸難以應付更加增長的傳輸及運算速度需求。而隨著大型AI模型的興起,所對應乘載這些大型神經網路模型的伺服器在追求更加強大的運算力的同時,也逐漸面臨龐大的能耗及散熱問題,傳統的氣冷式機房已經逐漸無法應付新一代GPU伺服器的散熱,正在邁向液冷式的機房。而這些而大型模型中的神經網路所進行的矩陣運算,也可以使用光來進行運算,這項技術被稱為光子處理器(photonic processor)、神經光子技術(neural-photonic)或光神經網路(optical neural network),透過光取代電來進行運算,可以大幅降低功耗並提升運算速度,並能實現即時平行運算,可望可以透過此技術突破目前神經網路所面對的計算速度以及能耗問題 [1-4]。

使用光來進行光神經網路運算其實並不是一個很新的概念,在多年前就已經有被人提出,使用多個馬赫-曾德爾干涉儀(Mach-Zehnder interferometer, MZI)光交換器組合就可以等效成一個全連階層(fully connect layer)的神經網路,但是光路架構龐大因此實用性不高,而近年來矽光子技術(silicon photonics)的興起提供了一個很好的平台給光神經網路,矽光子技術是以矽做為光波導材料,結合半導體製程技術將各種光電元件整合到單一積體化晶片上,具有低功耗、小尺寸,且與CMOS (complementary-metal-oxide-semiconductor)製程工度相容等優點。因此透過矽光子技術,得以將龐大的光路積體化到一塊微小的晶片中,使得龐大的MZI網路架構具備實用性的可能。

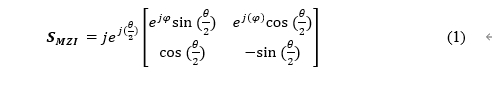

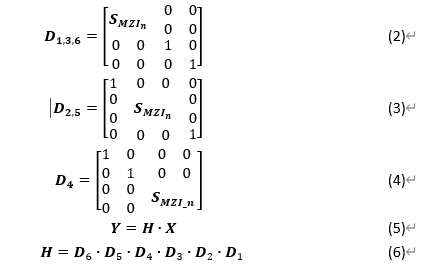

一個MZI光交換器的結構如圖1所示,分別由兩個3dB耦合器與兩個相位偏移器所構成,其變換矩陣(transformation matrix)由式(1)表示,其中θ與φ分別代表兩個相位偏移器的相位偏移量。

圖1. MZI光交換器基礎結構圖

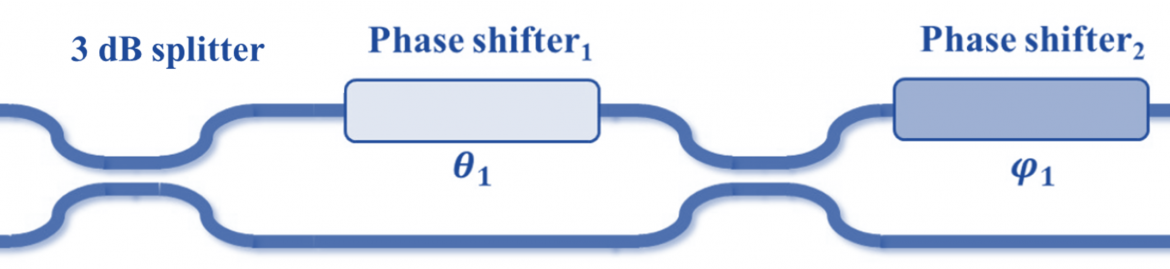

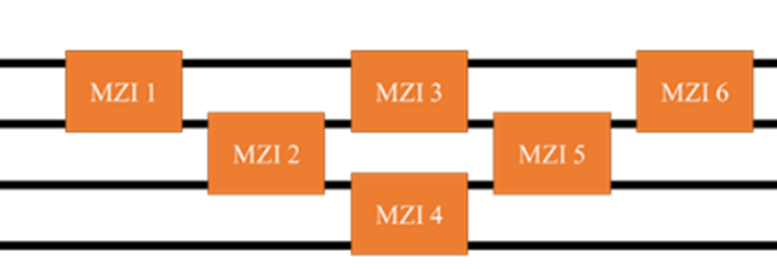

而藉由不同的MZI光交換器排列組合方式,可以使其成為一個 個神經元的全連階層,其中Reck mesh具有相對簡單的數學模型,其由 個MZI光交換器組合成一個 的全連階層,其MZI光交換器排列方式,由最下層一個MZI光交換器往上每層遞增,最上層MZI光交換器數量為N-1個,總計排列為N-1層。而每一個MZI光交換器的變換矩陣可以擴展成一個N維的希爾伯特空間(Hilbert space)矩陣,整個Reck mesh的運算相當於每一個MZI光交換器希爾伯特空間矩陣的連續相乘,從而得到一個與全連階層相似的矩陣運算。以一個如圖2的 reck mesh架構為例,將MZI光交換器由左到右,由上到下進行編號,可以得到每一個 MZI光交換器的希爾伯特空間矩陣如式(2)到(4)所示,而整個架構的矩陣運算則如式(5)和式(6)所示,其中X代表輸入矩陣,Y代表輸出矩陣。

圖2. reck mesh架構示意圖

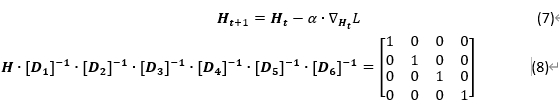

而訓練模型的過程可以使用與目前所用來訓練一般神經網路相同的演算法來對於網路來進行訓練,如梯度下降法(Gradient Decent),如式(7)所示,對於H矩陣中的參數進行更新,其中L代表損失函數(loss function), 代表模型學習速率(learning rate), 代表梯度運算符,t則代表當前的訓練週期(epoch)。而又因為H矩陣為線性變換矩陣的特性,將H矩陣對於每一個MZI光交換器的反矩陣進行連續相層,矩陣中的上三角與下三角區域中的每一個單元將逐漸變為零,最終成為一個單位矩陣,如式(8)所示。而在這個過程中可以得到多個多項式,再利用解多元多項式的運算來逐漸解出每一個MZI光交換器的與參數。

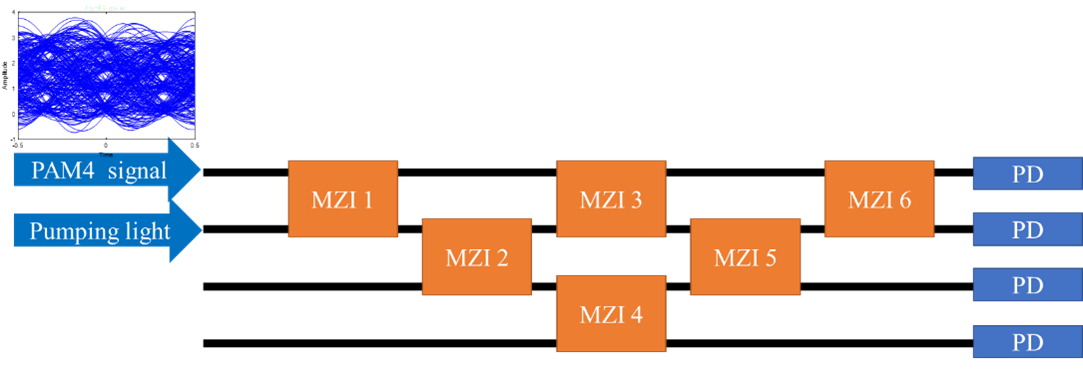

本實驗室團隊利用光神經網路的算法針對一組160 Gbit/s到240 Gbit/s的高失真PAM4訊號進行處理,所用來進行分類的訊號為使用頻寬為47 GHz的調製器所產生的高速PAM4訊號,由於調製器頻寬不足所導致具有嚴重的符碼間干擾(inter-symbol interference, ISI)的現象。所使用的模型架構如圖4所示,採用一個 的reck mesh架構,後端分別連接4個光偵測器(photodetector, PD)來接收訊號。而在輸入端除了輸入訊號之外,還會輸入一道額外的泵浦光(pumping light)來增加訊號的差異,要不然對於我們的神經網路系統來說,PAM4訊號4階不同的能量只是損耗的差別,難以分析出四個不同的能量位階所代表的訊號。

圖3. 對高失真PAM4訊號進行分類模型架構圖。

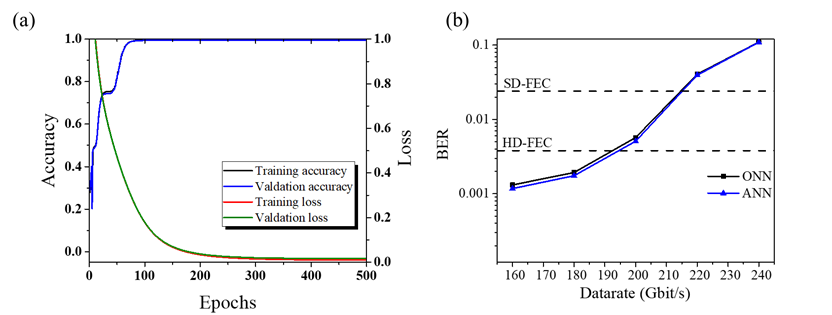

我們的模擬結果如圖4所示,圖4(a)為隨著訓練週期的損失函數與準確率圖,由圖可以看到在經過了約350訓練週期後損失函數達到收斂,並且能實現99%以上的分類準確率。圖4(b)則是不同傳輸速度的訊號經過光神經網路處理過後的誤碼率分析,由圖可以看到,我們的模型架構可以在200 Gbit/s的傳輸速度下滿足SD-FEC條件(BER=2.4 10-2),我們同時也是使用一個 的傳統類神經網路(ANN)運算模型來進行比較,可以發現兩條線幾乎重合,代表這種光神經網路能夠確實等效成一個只含有全連階層的類神經網路架構。

圖4. (a) 訓練週期對損失函數與準確率圖 (b) 不同傳輸速度在經光神經網路與一般傳統人工神經網路模型處理後的誤碼率分析。

在這個研究中,本團隊成功的利用了一個 的reck mesh架構對於高失真的PAM4訊號進行分類解析模擬,能將因為頻寬不足而產生嚴重失真的PAM4訊號,在160 Gbit/s到200 Gbit/s的情況下滿足SD-FEC的傳輸標準,相關研究結果有發表在Photonics期刊,並獲選當期封面故事(圖5)[5]。

圖5. 提出MZI的光學神經網路,被選為 Photonics, April 2024 封面故事

圖5. 提出MZI的光學神經網路,被選為 Photonics, April 2024 封面故事

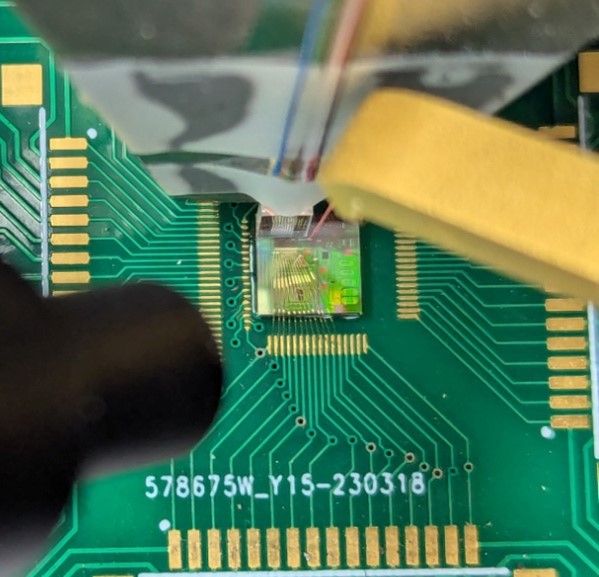

最近,我們與國外研究團隊合作開發可編程矽光子處理器(Programmable Silicon Photonics Processor)[6],該處理器可分開模態多工訊號,提高通道性能,並提高整體數據速率,圖6顯示使用光纖陣列和電偏壓來控制可編程矽光子處理器。

圖6. 可編程矽光子處理器(Programmable Silicon Photonics Processor) 實驗照片

參考

[1] W. Bogaerts, et al, “Programmable photonic circuits,” Nature, vol. 586, pp. 207–216, 2020.

[2] B. J. Shastri, et al, “Photonics for artificial intelligence and neuromorphic computing,” Nature Photonics, vol. 15, pp. 102–114, 2021.

[3] Y. Shen, et al, “Deep learning with coherent nanophotonic circuits,” Nature Photonics, vol. 11, pp. 441–446, 2017.

[4] X. Zhou, et al, “Silicon photonics for high-speed communications and photonic signal processing,” npj Nanophoton., vol. 1, pp. 27, 2024.

[5] T. Y. Hung, et al, “Regeneration of 200 Gbit/s PAM4 signal produced by silicon microring modulator (SiMRM) using Mach–Zehnder interferometer (MZI)-based optical neural network (ONN),” Photonics, vol. 11, pp. 349, 2024.

[6] D. YI, et al, "Unmixing data lanes in mode-division multiplexing optical fiber transmission using an integrated photonic processor," Journal of Lightwave Technology, vol. 42, pp. 287-292, 2024.